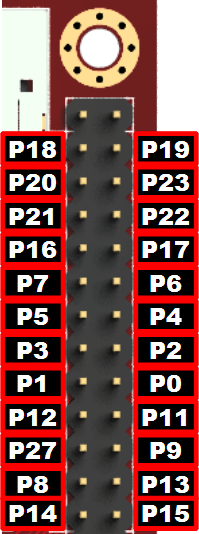

Ethernut 3 GPIO

Am Expansionport stehen folgende GPIO-Pins der CPU zur Verfügung:

| P0/TCLK0 | Dieser Pin ist nur mit der CPU verbunden und frei verfügbar. Im Peripheriemodus lässt sich der Pin als Takteingang für Counter/Timer 0 verwenden. |

|

| P1/TIOA0 | Dieser Pin ist nur mit der CPU verbunden und frei verfügbar. | |

| P2/TIOB0 | Dieser Pin ist nur mit der CPU verbunden und frei verfügbar. | |

| P3/TCLK1 | Frei verfügbar. Im Peripheriemodus lässt sich der Pin als Takteingang für Counter/Timer 1 verwenden. | |

| P4/TIOA1 | Frei verfügbar | |

| P5/TIOB1 | Frei verfügbar | |

| P6/TCLK2 | Frei verfügbar. Im Peripheriemodus lässt sich der Pin als Takteingang für Counter/Timer 2 verwenden. | |

| P7/TIOA2 | Frei verfügbar | |

| P8/TIOB2 | Frei verfügbar | |

| P9/IRQ0 | CPLD Interrupt-Ausgang | |

| P11/IRQ2 | Frei verfügbar | |

| P12/FIQ | Frei verfügbar | |

| P13/SCK0 | Frei verfügbar | |

| P14/TXD0 | Transmit-Ausgang von USART0 | |

| P15/RXD0 | Receive-Eingang von USART0 | |

| P16 | I2C-Datenleitung | |

| P17 | I2C-Taktleitung | |

| P18 | Frei verfügbar (JP5) | |

| P19 | Frei verfügbar (JP5) | |

| P20/SCK1 | Frei verfügbar | |

| P21/TXD1 | Transmit-Ausgang von USART1 | |

| P22/RXD1 | Receive-Eingang von USART0 | |

| P23 | Frei verfügbar (JP5) | |

| P27/NCS3 | Frei verfügbar |