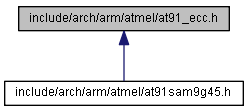

Go to the source code of this file.

ECC Control Register | |

| #define | ECC_CR_OFF 0x00000000 |

| Control register offset. | |

| #define | ECC_CR (ECC_BASE + ECC_CR_OFF) |

| Control register address. | |

| #define | ECC_RST 0x00000001 |

| Reset ECC parity registers. | |

| #define | ECC_SRST 0x00000002 |

| Software reset. | |

ECC Mode Register | |

| #define | ECC_MR_OFF 0x00000004 |

| Mode register offset. | |

| #define | ECC_MR (ECC_BASE + ECC_MR_OFF) |

| Mode register address. | |

| #define | ECC_PAGESIZE 0x00000003 |

| NAND flash page size mask. | |

| #define | ECC_PAGESIZE_528 0x00000000 |

| NAND flash page size is 528 words. | |

| #define | ECC_PAGESIZE_1056 0x00000001 |

| NAND flash page size is 1056 words. | |

| #define | ECC_PAGESIZE_2112 0x00000002 |

| NAND flash page size is 2112 words. | |

| #define | ECC_PAGESIZE_4224 0x00000003 |

| NAND flash page size is 4224 words. | |

| #define | ECC_TYPECORREC 0x00000030 |

| Type of correction mask. | |

| #define | ECC_TYPECORREC_0 0x00000000 |

| 1 bit correction. | |

| #define | ECC_TYPECORREC_1 0x00000010 |

| 1 bit correction for 256 data bytes. | |

| #define | ECC_TYPECORREC_2 0x00000020 |

| 1 bit correction for 512 data bytes. | |

ECC Status Registers | |

| #define | ECC_SR1_OFF 0x00000008 |

| Status register 1 offset. | |

| #define | ECC_SR1 (ECC_BASE + ECC_SR1_OFF) |

| Status register 1 address. | |

| #define | ECC_SR2_OFF 0x00000014 |

| Status register 2 offset. | |

| #define | ECC_SR2 (ECC_BASE + ECC_SR2_OFF) |

| Status register 2 address. | |

| #define | ECC_RECERR(i) (1 << (i * 4)) |

| Recoverable error. | |

| #define | ECC_ECCERR(i) (2 << (i * 4)) |

| Single bit error. | |

| #define | ECC_MULERR(i) (4 << (i * 4)) |

| Multiple errors. | |

ECC Parity Registers | |

| #define | ECC_PR0_OFF 0x0000000C |

| Parity register 0 offset. | |

| #define | ECC_PR0 (ECC_BASE + ECC_PR0_OFF) |

| Parity register 0 address. | |

| #define | ECC_PR1_OFF 0x00000010 |

| Parity register 1 offset. | |

| #define | ECC_PR1 (ECC_BASE + ECC_PR1_OFF) |

| Parity register 1 address. | |

| #define | ECC_PR(i) (ECC_BASE + 0x18 + (((i) - 2) * 4)) |

| Parity registers 2 to 15 address. | |

| #define | ECC_BITADDR0 0x0000000F |

| Corrupted bit offset mask. | |

| #define | ECC_BITADDR0_LSB 0 |

| Corrupted bit offset LSB. | |

| #define | ECC_BITADDR 0x00000007 |

| Corrupted bit offset mask, 8-bit word. | |

| #define | ECC_BITADDR_LSB 0 |

| Corrupted bit offset LSB, 8-bit word. | |

| #define | ECC_WORDADDR0 0x0000FFF0 |

| Corrupted bit word offset mask, type 1. | |

| #define | ECC_WORDADDR0_LSB 4 |

| Corrupted bit word offset LSB, type 1. | |

| #define | ECC_WORDADDR 0x0000FFF8 |

| Corrupted bit word offset mask. | |

| #define | ECC_WORDADDR_LSB 3 |

| Corrupted bit word offset LSB. | |

| #define | ECC_NPARITY1 0x0000FFFF |

| Parity 1 mask. | |

| #define | ECC_NPARITY1_LSB 0 |

| Parity 1 LSB. | |

| #define | ECC_NPARITY 0x00FFF000 |

| Parity mask. | |

| #define | ECC_NPARITY_LSB 12 |

| Parity LSB. | |

ECC Version Register | |

| #define | ECC_VR_OFF 0x000000FC |

| #define | ECC_VR (ECC_BASE + ECC_VR_OFF) |

| #define ECC_VR_OFF 0x000000FC |

Definition at line 110 of file at91_ecc.h.

| #define ECC_VR (ECC_BASE + ECC_VR_OFF) |

Definition at line 111 of file at91_ecc.h.