Programmable clock generator with three PLLs. More...

|

Defines | |

| #define | CY2239X_CLKA 0 |

| Clock A output. | |

| #define | CY2239X_CLKB 1 |

| Clock B output. | |

| #define | CY2239X_CLKC 2 |

| Clock C output. | |

| #define | CY2239X_CLKD 3 |

| Clock D output. | |

| #define | CY2239X_CLKE 4 |

| Clock E output. | |

| #define | CY2239X_REF 0 |

| Reference clock identifier. | |

| #define | CY2239X_PLL1 1 |

| PLL1 identifier. | |

| #define | CY2239X_PLL2 2 |

| PLL2 identifier. | |

| #define | CY2239X_PLL3 3 |

| PLL3 identifier. | |

| #define | I2C_SLA_PLL 0x69 |

| I2C address. | |

| #define | NUT_PLL_FREF 25000000UL |

| Base frequency. | |

Functions | |

| int | Cy2239xGetPll (int clk) |

| Get the PLL connected to the specified output. | |

| int | Cy2239xSetPll (int clk, int pll) |

| Connect a specified PLL to a specified output. | |

| int | Cy2239xGetDivider (int clk, int fctrl) |

| Get the current divider value of the specified output. | |

| int | Cy2239xSetDivider (int clk, int sel, int val) |

| Set the divider value of the specified output. | |

| int | Cy2239xPllEnable (int pll, int fctrl, int ena) |

| Enable or disable a specified PLL. | |

| uint32_t | Cy2239xPllGetFreq (int pll, int fctrl) |

| Get the current frequency of a specified PLL. | |

| int | Cy2239xPllSetFreq (int pll, int fctrl, unsigned int pval, unsigned int poff, unsigned int qval, unsigned int fval) |

| Set the frequency of a specified PLL. | |

| uint32_t | Cy2239xGetFreq (int clk, int fctrl) |

| Get the frequency of a specified output. | |

Programmable clock generator with three PLLs.

#include <dev/cy2239x.h>

The CY22393 chip is used in the Ethernut 3 reference design. It provides three unique frequencies on six outputs, with an additional divider at five outputs.

The following outputs are used on Ethernut 3:

| #define CY2239X_CLKA 0 |

| #define CY2239X_CLKB 1 |

Clock B output.

On Ethernut 3 this is output drives the GCK1 input of the CPLD, if R6 is mounted (default).

Definition at line 72 of file cy2239x.h.

Referenced by Cy2239xGetDivider(), Cy2239xGetFreq(), and Cy2239xSetDivider().

| #define CY2239X_CLKC 2 |

| #define CY2239X_CLKD 3 |

| #define CY2239X_CLKE 4 |

Clock E output.

On Ethernut 3 this is output drives the GCK3 input of the CPLD, if R104 is mounted and R4 is not mounted. By default R104 is not mounted, but R4 is.

Definition at line 94 of file cy2239x.h.

Referenced by Cy2239xGetDivider(), Cy2239xGetFreq(), Cy2239xGetPll(), Cy2239xSetDivider(), and Cy2239xSetPll().

| #define CY2239X_REF 0 |

Reference clock identifier.

Definition at line 98 of file cy2239x.h.

Referenced by Cy2239xGetFreq().

| #define CY2239X_PLL1 1 |

PLL1 identifier.

The output of PLL1 can be connected to any output divider. Clock E output is fixed to PLL1.

Definition at line 105 of file cy2239x.h.

Referenced by Cy2239xGetFreq(), Cy2239xPllEnable(), Cy2239xPllGetFreq(), Cy2239xPllSetFreq(), and Cy2239xSetPll().

| #define CY2239X_PLL2 2 |

PLL2 identifier.

The output of PLL2 can be connected to the output divider of clock A, B, C or D.

Definition at line 112 of file cy2239x.h.

Referenced by Cy2239xGetFreq(), Cy2239xPllEnable(), Cy2239xPllGetFreq(), and Cy2239xPllSetFreq().

| #define CY2239X_PLL3 3 |

PLL3 identifier.

The output of PLL3 can be connected to the output divider of clock A, B, C or D.

Definition at line 119 of file cy2239x.h.

Referenced by Cy2239xGetFreq(), Cy2239xPllEnable(), Cy2239xPllGetFreq(), and Cy2239xPllSetFreq().

| #define I2C_SLA_PLL 0x69 |

I2C address.

Definition at line 74 of file cy2239x.c.

Referenced by Cy2239xGetDivider(), Cy2239xGetFreq(), Cy2239xGetPll(), Cy2239xPllEnable(), Cy2239xPllGetFreq(), Cy2239xPllSetFreq(), Cy2239xSetDivider(), and Cy2239xSetPll().

| #define NUT_PLL_FREF 25000000UL |

Base frequency.

Frequency of the attached crystal. On Ethernut 3 a 25 MHz crystal is used.

Definition at line 83 of file cy2239x.c.

Referenced by Cy2239xGetFreq(), and Cy2239xPllGetFreq().

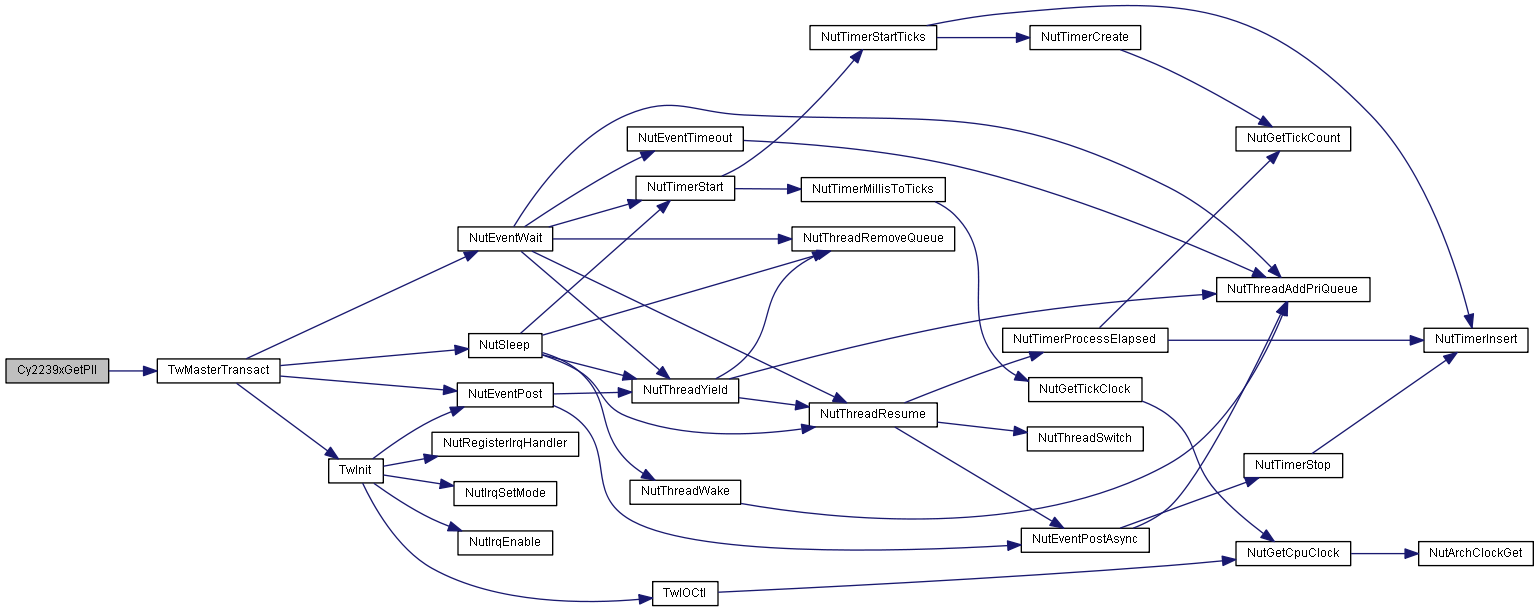

| int Cy2239xGetPll | ( | int | clk | ) |

Get the PLL connected to the specified output.

| clk | Specifies the output. 0 = ClkA, 1 = ClkB etc. |

The following code fragment stores the number of the PLL connected to Clock Output C in the variable pll.

int pll; pll = Cy2239xGetPll(CY2239X_CLKC);

Definition at line 124 of file cy2239x.c.

References CY2239X_CLKE, I2C_SLA_PLL, NUT_WAIT_INFINITE, and TwMasterTransact().

| int Cy2239xSetPll | ( | int | clk, |

| int | pll | ||

| ) |

Connect a specified PLL to a specified output.

| clk | Specifies the output. 0 = ClkA, 1 = ClkB etc. |

| pll | 1 - 3 for PLL1 - PLL3 resp. or 0 to select the reference clock. |

The following code can be used to connect PLL3 to Clock Output B.

if (Cy2239xSetPll(CY2239X_CLKB, CY2239X_PLL3)) { printf("Failed to select PLL3 for Clock B\n"); }

Definition at line 159 of file cy2239x.c.

References CY2239X_CLKE, CY2239X_PLL1, I2C_SLA_PLL, NUT_WAIT_INFINITE, and TwMasterTransact().

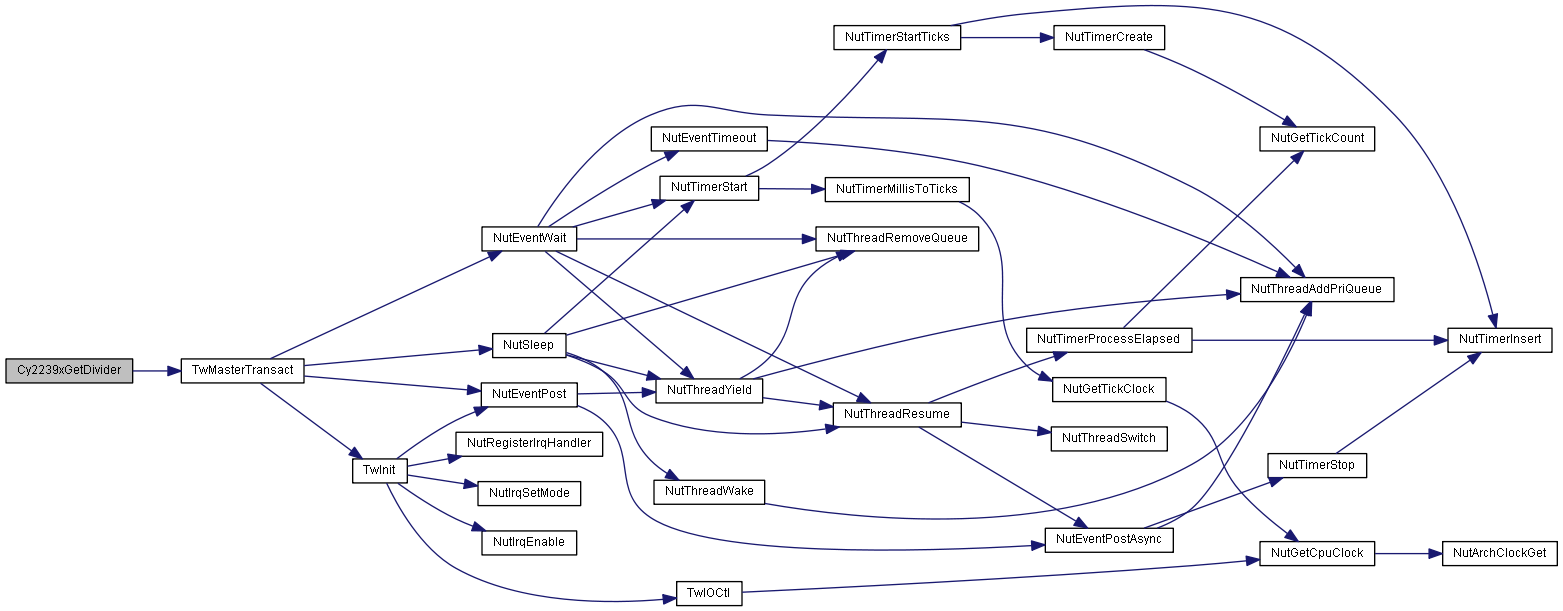

| int Cy2239xGetDivider | ( | int | clk, |

| int | fctrl | ||

| ) |

Get the current divider value of the specified output.

| clk | Specifies the output. 0 = ClkA, 1 = ClkB etc. |

| fctrl | Frequency control input status, only valid for clock A and B. Otherwise this parameter is ignored. For Ethernut 3 the inputs S0 and S1 are high and S2 is connected to the CPLD. Thus, this value is either 3 if control input S2 is low or 7 if S2 is set high (default). |

Definition at line 199 of file cy2239x.c.

References CY2239X_CLKB, CY2239X_CLKE, I2C_SLA_PLL, NUT_WAIT_INFINITE, and TwMasterTransact().

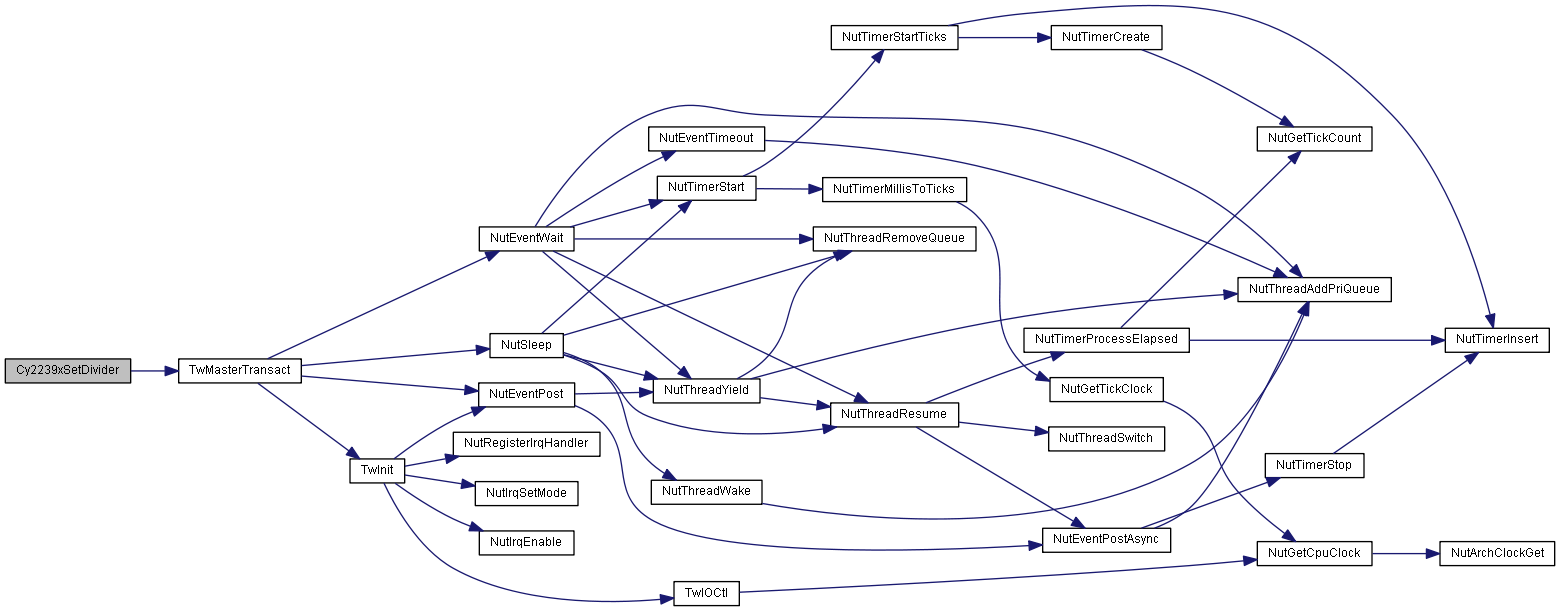

| int Cy2239xSetDivider | ( | int | clk, |

| int | sel, | ||

| int | val | ||

| ) |

Set the divider value of the specified output.

Clock A through D provide a 7-bit output divider, while the Clock E divider is fixed to 0 (off), 2, 3 or 4.

Changing the divider value of an active output may cause a glitch on the output.

| clk | Specifies the output. 0 = ClkA, 1 = ClkB etc. |

| sel | Divider select for Clock A and B, either 0 or 1. For other outputs this parameter is ignored. |

| val | New divider value to set. A value of zero powers down the divider and forces the output to three-state. |

Definition at line 262 of file cy2239x.c.

References CY2239X_CLKB, CY2239X_CLKE, I2C_SLA_PLL, NUT_WAIT_INFINITE, and TwMasterTransact().

| int Cy2239xPllEnable | ( | int | pll, |

| int | fctrl, | ||

| int | ena | ||

| ) |

Enable or disable a specified PLL.

| pll | Set to 1 - 3 for PLL1 - PLL3 resp. |

| fctrl | Frequency control input status, only used for PLL1. Otherwise this parameter is ignored. For Ethernut 3 the inputs S0 and S1 are high and S2 is connected to the CPLD. Thus, this value is either 3 if control input S2 is low or 7 if S2 is set to high. |

| ena | 0 will disable the PLL, 1 will enable it. Any other value may be used to query the current status. |

The following code shuts down PLL2 and Clock Output A. On Ethernut 3 this will remove the clock from the Ethernet Controller.

if (Cy2239xSetDivider(CY2239X_CLKA, 1, 0)) { printf("Failed to disable ClkA Divider 1\n"); } if (Cy2239xPllEnable(CY2239X_PLL2, 7, 0)) { printf("Failed to disable PLL2\n"); }

Definition at line 328 of file cy2239x.c.

References CY2239X_PLL1, CY2239X_PLL2, CY2239X_PLL3, I2C_SLA_PLL, NUT_WAIT_INFINITE, and TwMasterTransact().

Referenced by Cy2239xPllSetFreq().

| uint32_t Cy2239xPllGetFreq | ( | int | pll, |

| int | fctrl | ||

| ) |

Get the current frequency of a specified PLL.

| pll | 1 - 3 for PLL1 - PLL3 resp. or 0 to query the reference clock. |

| fctrl | Frequency control input status, only used for PLL1. Otherwise this parameter is ignored. For Ethernut 3 the inputs S0 and S1 are high and S2 is connected to the CPLD. Thus, this value is either 3 if control input S2 is low or 7 if S2 is set to high. |

Use the following code to retrieve the reference clock:

uint32_t fref; fref = Cy2239xPllGetFreq(CY2239X_REF, 7);

Definition at line 383 of file cy2239x.c.

References CY2239X_PLL1, CY2239X_PLL2, CY2239X_PLL3, I2C_SLA_PLL, NUT_PLL_FREF, NUT_WAIT_INFINITE, and TwMasterTransact().

| int Cy2239xPllSetFreq | ( | int | pll, |

| int | fctrl, | ||

| unsigned int | pval, | ||

| unsigned int | poff, | ||

| unsigned int | qval, | ||

| unsigned int | fval | ||

| ) |

Set the frequency of a specified PLL.

If the PLL is enabled, it will be temporarily disabled.

The resulting frequency can calculated by

F = Fref * (2 * (Pval + 3) + Poff) / (Qval + 2)

It is recommended to use Cypress' CyClocksRT utility for calculating the best parameter values.

| pll | 1 - 3 for PLL1 - PLL3 resp. |

| fctrl | Frequency control input status, only valid for clock A and B. Otherwise this parameter is ignored. For Ethernut 3 the inputs S0 and S1 are high and S2 is connected to the CPLD. Thus, this value is either 3 if control input S2 is low or 7 if S2 is set to high. |

| pval | 10-bit multiplier. |

| poff | 1-bit offset. |

| qval | 8-bit divider. |

| fval | 2-bit loop filter value. This value corresponds to the multiplier value and guarantess the PLL stability. |

Definition at line 440 of file cy2239x.c.

References CY2239X_PLL1, CY2239X_PLL2, CY2239X_PLL3, Cy2239xPllEnable(), I2C_SLA_PLL, NUT_WAIT_INFINITE, and TwMasterTransact().

| uint32_t Cy2239xGetFreq | ( | int | clk, |

| int | fctrl | ||

| ) |

Get the frequency of a specified output.

On Ethernut 3 Clock A provides the Ethernet Controller clock and Clock C is used as the CPU clock.

PLL1 provides two configurations, selectable by the external input S2, which might be controlled by the Ethernut 3 CPLD. However, NPL version 2 doesn't allow to modify the S2 line, but holds it at a fixed high level.

| clk | Specifies the output. 0 = ClkA, 1 = ClkB etc. |

| fctrl | Frequency control input status, only valid for clock A and B. Otherwise this parameter is ignored. For Ethernut 3 the inputs S0 and S1 are high and S2 is connected to the CPLD. Thus, this value is either 3 if control input S2 is low or 7 if S2 is set to high. |

The following code can be used to query the main CPU clock on the Ethernut 3 board.

uint32_t fcpu; fcpu = Cy2239xGetFreq(CY2239X_CLKC, 7);

Definition at line 506 of file cy2239x.c.

References CY2239X_CLKB, CY2239X_CLKE, CY2239X_PLL1, CY2239X_PLL2, CY2239X_PLL3, CY2239X_REF, I2C_SLA_PLL, NUT_PLL_FREF, NUT_WAIT_INFINITE, and TwMasterTransact().