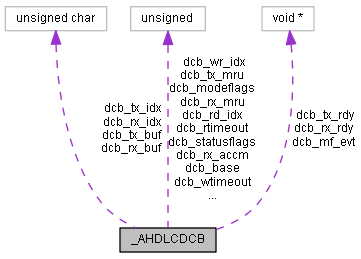

Asynchronous HDLC device information structure. More...

#include <dev/ahdlc.h>

Data Fields | |

| uint32_t | dcb_modeflags |

| Mode flags. | |

| uint32_t | dcb_statusflags |

| Status flags. | |

| uint32_t | dcb_rtimeout |

| Read timeout. | |

| uint32_t | dcb_wtimeout |

| Write timeout. | |

| HANDLE | dcb_tx_rdy |

| Queue of threads waiting for output buffer empty. | |

| HANDLE | dcb_rx_rdy |

| Queue of threads waiting for a character in the input buffer. | |

| uint8_t | dcb_base |

| Hardware base address. | |

| volatile uint8_t * | dcb_rx_buf |

| Input buffer. | |

| volatile uint8_t | dcb_rx_idx |

| Input buffer index for next incoming byte. | |

| uint8_t | dcb_rd_idx |

| Input buffer index for next byte to read. | |

| uint8_t * | dcb_tx_buf |

| Output buffer. | |

| volatile uint8_t | dcb_tx_idx |

| Output buffer index for next outgoing byte. | |

| uint8_t | dcb_wr_idx |

| Output buffer index for next byte to write. | |

| HANDLE | dcb_mf_evt |

| HDLC mode change event queue. | |

| uint32_t | dcb_rx_accm |

| 32-bit receive ACCM. | |

| uint32_t | dcb_tx_accm |

| 256-bit transmit ACCM. | |

| uint16_t | dcb_rx_mru |

| Maximum receive MRU. | |

| uint16_t | dcb_tx_mru |

| Maximum transmit MRU. | |

Asynchronous HDLC device information structure.

The start of this structure is equal to the UARTDCB structure.

Mode flags.

Definition at line 86 of file ahdlc.h.

Referenced by AhdlcAt91IOCtl(), AhdlcAvrIOCtl(), AhdlcOutput(), and AhdlcRx().

Read timeout.

Definition at line 94 of file ahdlc.h.

Referenced by AhdlcAt91IOCtl(), AhdlcAt91Read(), AhdlcAvrIOCtl(), AhdlcAvrRead(), and AhdlcRx().

Write timeout.

Definition at line 98 of file ahdlc.h.

Referenced by AhdlcAt91IOCtl(), and AhdlcAvrIOCtl().

Queue of threads waiting for a character in the input buffer.

Threads are added to this queue when the output buffer is empty.

Definition at line 112 of file ahdlc.h.

Referenced by AhdlcAt91IOCtl(), AhdlcAt91Read(), AhdlcAvrIOCtl(), AhdlcAvrRead(), and AhdlcRx().

Hardware base address.

This is a copy of the base address in the NUTDEVICE structure and required by the interrupt routine.

Definition at line 119 of file ahdlc.h.

Referenced by AhdlcAt91Init(), AhdlcAt91IOCtl(), and AhdlcAvrInit().

| volatile uint8_t* _AHDLCDCB::dcb_rx_buf |

Input buffer.

This buffer is filled by the the receiver interrupt, so the contents of the buffer is volatile.

Definition at line 126 of file ahdlc.h.

Referenced by AhdlcAt91Init(), AhdlcAt91Read(), AhdlcAvrInit(), AhdlcAvrRead(), and AhdlcRx().

| volatile uint8_t _AHDLCDCB::dcb_rx_idx |

Input buffer index for next incoming byte.

This volatile index is incremented by the receiver interrupt.

Definition at line 132 of file ahdlc.h.

Referenced by AhdlcAt91Read(), AhdlcAvrRead(), and AhdlcRx().

Input buffer index for next byte to read.

Definition at line 136 of file ahdlc.h.

Referenced by AhdlcAt91Read(), AhdlcAvrRead(), and AhdlcRx().

Output buffer.

Definition at line 140 of file ahdlc.h.

Referenced by AhdlcAt91Init(), and AhdlcAvrInit().

| volatile uint8_t _AHDLCDCB::dcb_tx_idx |

HDLC mode change event queue.

The frame receiver thread is waiting on this queue until the device is switched to HDLC mode.

Definition at line 157 of file ahdlc.h.

Referenced by AhdlcAt91IOCtl(), AhdlcAvrIOCtl(), and AhdlcRx().

256-bit transmit ACCM.

Definition at line 165 of file ahdlc.h.

Referenced by AhdlcAt91Init(), AhdlcAvrInit(), and AhdlcAvrIOCtl().

Maximum receive MRU.

Definition at line 169 of file ahdlc.h.

Referenced by AhdlcAt91Init(), AhdlcAvrInit(), AhdlcAvrIOCtl(), and AhdlcRx().

Maximum transmit MRU.

Definition at line 173 of file ahdlc.h.

Referenced by AhdlcAt91Init(), AhdlcAvrInit(), AhdlcAvrIOCtl(), and AhdlcOutput().