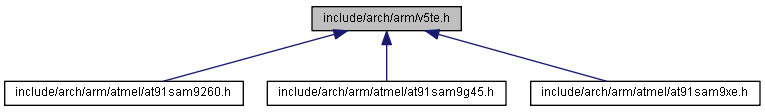

ARM9 specific features. More...

Go to the source code of this file.

Defines | |

| #define | CP15_CR1_M_BIT 0 |

| Enables MMU. | |

| #define | CP15_CR1_A_BIT 1 |

| Enables alignment fault. | |

| #define | CP15_CR1_C_BIT 2 |

| Enables data cache. | |

| #define | CP15_CR1_B_BIT 7 |

| Enables big endian operation. | |

| #define | CP15_CR1_S_BIT 8 |

| Enables system protection. | |

| #define | CP15_CR1_R_BIT 9 |

| Enables ROM protection. | |

| #define | CP15_CR1_I_BIT 12 |

| Enables instruction cache. | |

| #define | CP15_CR1_V_BIT 13 |

| Enables high exception vectors. | |

| #define | CP15_CR1_RR_BIT 14 |

| Enables round robin replacement strategy. | |

| #define | CP15_CR1_L4_BIT 15 |

| Enables MMU. | |

ARM9 specific features.

* $Id: v5te.h 2475 2009-02-17 09:35:05Z haraldkipp $ *

Definition in file v5te.h.

| #define CP15_CR1_RR_BIT 14 |