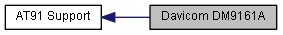

Davicom DM9161A registers. More...

|

Data Structures | |

| struct | _EMACINFO |

| Network interface controller information structure. More... | |

| struct | _RxTdDescriptor |

Defines | |

| #define | NIC_PHY_BMCR 0x00 |

| Basic mode control register. | |

| #define | NIC_PHY_BMCR_COLTEST 0x0080 |

| Collision test. | |

| #define | NIC_PHY_BMCR_FDUPLEX 0x0100 |

| Full duplex mode. | |

| #define | NIC_PHY_BMCR_ANEGSTART 0x0200 |

| Restart auto negotiation. | |

| #define | NIC_PHY_BMCR_ISOLATE 0x0400 |

| Isolate from MII. | |

| #define | NIC_PHY_BMCR_PWRDN 0x0800 |

| Power-down. | |

| #define | NIC_PHY_BMCR_ANEGENA 0x1000 |

| Enable auto negotiation. | |

| #define | NIC_PHY_BMCR_100MBPS 0x2000 |

| Select 100 Mbps. | |

| #define | NIC_PHY_BMCR_LOOPBACK 0x4000 |

| Enable loopback mode. | |

| #define | NIC_PHY_BMCR_RESET 0x8000 |

| Software reset. | |

| #define | NIC_PHY_BMSR 0x01 |

| Basic mode status register. | |

| #define | NIC_PHY_BMSR_ANCOMPL 0x0020 |

| Auto negotiation complete. | |

| #define | NIC_PHY_BMSR_LINKSTAT 0x0004 |

| Link status. | |

| #define | NIC_PHY_ID1 0x02 |

| PHY identifier register 1. | |

| #define | NIC_PHY_ID2 0x03 |

| PHY identifier register 2. | |

| #define | NIC_PHY_ANAR 0x04 |

| Auto negotiation advertisement register. | |

| #define | NIC_PHY_ANLPAR 0x05 |

| Auto negotiation link partner availability register. | |

| #define | NIC_PHY_ANEG_NP 0x8000 |

| Next page available. | |

| #define | NIC_PHY_ANEG_ACK 0x4000 |

| Ability data reception acknowledged. | |

| #define | NIC_PHY_ANEG_RF 0x2000 |

| Remote fault. | |

| #define | NIC_PHY_ANEG_FCS 0x0400 |

| Flow control supported. | |

| #define | NIC_PHY_ANEG_T4 0x0200 |

| 100BASE-T4 supported. | |

| #define | NIC_PHY_ANEG_TX_FDX 0x0100 |

| 100BASE-T full duplex supported. | |

| #define | NIC_PHY_ANEG_TX_HDX 0x0080 |

| 100BASE-T half duplex supported. | |

| #define | NIC_PHY_ANEG_10_FDX 0x0040 |

| 10BASE-T full duplex supported. | |

| #define | NIC_PHY_ANEG_10_HDX 0x0020 |

| 10BASE-T half duplex supported. | |

| #define | NIC_PHY_ANEG_BINSEL 0x001F |

| Binary encoded protocol selector. | |

| #define | NIC_PHY_ANER 0x06 |

| Auto negotiation expansion register. | |

| #define | NIC_PHY_BMCR 0x00 |

| Basic mode control register. | |

| #define | NIC_PHY_BMCR_COLTEST 0x0080 |

| Collision test. | |

| #define | NIC_PHY_BMCR_FDUPLEX 0x0100 |

| Full duplex mode. | |

| #define | NIC_PHY_BMCR_ANEGSTART 0x0200 |

| Restart auto negotiation. | |

| #define | NIC_PHY_BMCR_ISOLATE 0x0400 |

| Isolate from MII. | |

| #define | NIC_PHY_BMCR_PWRDN 0x0800 |

| Power-down. | |

| #define | NIC_PHY_BMCR_ANEGENA 0x1000 |

| Enable auto negotiation. | |

| #define | NIC_PHY_BMCR_100MBPS 0x2000 |

| Select 100 Mbps. | |

| #define | NIC_PHY_BMCR_LOOPBACK 0x4000 |

| Enable loopback mode. | |

| #define | NIC_PHY_BMCR_RESET 0x8000 |

| Software reset. | |

| #define | NIC_PHY_BMSR 0x01 |

| Basic mode status register. | |

| #define | NIC_PHY_BMSR_ANCOMPL 0x0020 |

| Auto negotiation complete. | |

| #define | NIC_PHY_BMSR_LINKSTAT 0x0004 |

| Link status. | |

| #define | NIC_PHY_ID1 0x02 |

| PHY identifier register 1. | |

| #define | NIC_PHY_ID2 0x03 |

| PHY identifier register 2. | |

| #define | NIC_PHY_ANAR 0x04 |

| Auto negotiation advertisement register. | |

| #define | NIC_PHY_ANLPAR 0x05 |

| Auto negotiation link partner availability register. | |

| #define | NIC_PHY_ANER 0x06 |

| Auto negotiation expansion register. | |

| #define | NIC_PHY_BMCR 0x00 |

| Basic mode control register. | |

| #define | NIC_PHY_BMCR_COLTEST 0x0080 |

| Collision test. | |

| #define | NIC_PHY_BMCR_FDUPLEX 0x0100 |

| Full duplex mode. | |

| #define | NIC_PHY_BMCR_ANEGSTART 0x0200 |

| Restart auto negotiation. | |

| #define | NIC_PHY_BMCR_ISOLATE 0x0400 |

| Isolate from MII. | |

| #define | NIC_PHY_BMCR_PWRDN 0x0800 |

| Power-down. | |

| #define | NIC_PHY_BMCR_ANEGENA 0x1000 |

| Enable auto negotiation. | |

| #define | NIC_PHY_BMCR_100MBPS 0x2000 |

| Select 100 Mbps. | |

| #define | NIC_PHY_BMCR_LOOPBACK 0x4000 |

| Enable loopback mode. | |

| #define | NIC_PHY_BMCR_RESET 0x8000 |

| Software reset. | |

| #define | NIC_PHY_BMSR 0x01 |

| Basic mode status register. | |

| #define | NIC_PHY_BMSR_ANCOMPL 0x0020 |

| Auto negotiation complete. | |

| #define | NIC_PHY_BMSR_LINKSTAT 0x0004 |

| Link status. | |

| #define | NIC_PHY_ID1 0x02 |

| PHY identifier register 1. | |

| #define | NIC_PHY_ID2 0x03 |

| PHY identifier register 2. | |

| #define | NIC_PHY_ANAR 0x04 |

| Auto negotiation advertisement register. | |

| #define | NIC_PHY_ANLPAR 0x05 |

| Auto negotiation link partner availability register. | |

| #define | NIC_PHY_ANEG_NP 0x8000 |

| Next page available. | |

| #define | NIC_PHY_ANEG_ACK 0x4000 |

| Ability data reception acknowledged. | |

| #define | NIC_PHY_ANEG_RF 0x2000 |

| Remote fault. | |

| #define | NIC_PHY_ANEG_FCS 0x0400 |

| Flow control supported. | |

| #define | NIC_PHY_ANEG_T4 0x0200 |

| 100BASE-T4 supported. | |

| #define | NIC_PHY_ANEG_TX_FDX 0x0100 |

| 100BASE-T full duplex supported. | |

| #define | NIC_PHY_ANEG_TX_HDX 0x0080 |

| 100BASE-T half duplex supported. | |

| #define | NIC_PHY_ANEG_10_FDX 0x0040 |

| 10BASE-T full duplex supported. | |

| #define | NIC_PHY_ANEG_10_HDX 0x0020 |

| 10BASE-T half duplex supported. | |

| #define | NIC_PHY_ANEG_BINSEL 0x001F |

| Binary encoded protocol selector. | |

| #define | NIC_PHY_ANER 0x06 |

| Auto negotiation expansion register. | |

| #define | NIC_PHY_ADDR 0 |

| PHY address. | |

| #define | NIC_PHY_UID 0xffffffff |

| #define | PHY_MODE_RMII |

Typedefs | |

| typedef struct _EMACINFO | EMACINFO |

| Network interface controller information type. | |

| typedef struct _RxTdDescriptor | RxTdDescriptor |

Advertisement control register. | |

| #define | NIC_PHY_ADVERTISE_SLCT 0x001f |

| Selector bits. | |

| #define | NIC_PHY_ADVERTISE_CSMA 0x0001 |

| Only selector supported. | |

| #define | NIC_PHY_ADVERTISE_10HALF 0x0020 |

| Try for 10mbps half-duplex. | |

| #define | NIC_PHY_ADVERTISE_1000XFULL 0x0020 |

| Try for 1000BASE-X full-duplex. | |

| #define | NIC_PHY_ADVERTISE_10FULL 0x0040 |

| Try for 10mbps full-duplex. | |

| #define | NIC_PHY_ADVERTISE_1000XHALF 0x0040 |

| Try for 1000BASE-X half-duplex. | |

| #define | NIC_PHY_ADVERTISE_100HALF 0x0080 |

| Try for 100mbps half-duplex. | |

| #define | NIC_PHY_ADVERTISE_1000XPAUSE 0x0080 |

| Try for 1000BASE-X pause. | |

| #define | NIC_PHY_ADVERTISE_100FULL 0x0100 |

| Try for 100mbps full-duplex. | |

| #define | NIC_PHY_ADVERTISE_1000XPSE_ASYM 0x0100 |

| Try for 1000BASE-X asym pause. | |

| #define | NIC_PHY_ADVERTISE_100BASE4 0x0200 |

| Try for 100mbps 4k packets. | |

| #define | NIC_PHY_ADVERTISE_PAUSE_CAP 0x0400 |

| Try for pause. | |

| #define | NIC_PHY_ADVERTISE_PAUSE_ASYM 0x0800 |

| Try for asymetric pause. | |

| #define | NIC_PHY_ADVERTISE_RESV 0x1000 |

| Unused... | |

| #define | NIC_PHY_ADVERTISE_RFAULT 0x2000 |

| Say we can detect faults. | |

| #define | NIC_PHY_ADVERTISE_LPACK 0x4000 |

| Ack link partners response. | |

| #define | NIC_PHY_ADVERTISE_NPAGE 0x8000 |

| Next page bit. | |

| #define | NIC_PHY_ADVERTISE_FULL (NIC_PHY_ADVERTISE_100FULL | NIC_PHY_ADVERTISE_10FULL | NIC_PHY_ADVERTISE_CSMA) |

| #define | NIC_PHY_ADVERTISE_ALL |

Davicom DM9161A registers.

| #define NIC_PHY_BMCR 0x00 |

Basic mode control register.

Definition at line 145 of file at91_emac.c.

| #define NIC_PHY_BMCR_COLTEST 0x0080 |

Collision test.

Definition at line 146 of file at91_emac.c.

| #define NIC_PHY_BMCR_FDUPLEX 0x0100 |

Full duplex mode.

Definition at line 147 of file at91_emac.c.

| #define NIC_PHY_BMCR_ANEGSTART 0x0200 |

Restart auto negotiation.

Definition at line 148 of file at91_emac.c.

| #define NIC_PHY_BMCR_ISOLATE 0x0400 |

Isolate from MII.

Definition at line 149 of file at91_emac.c.

| #define NIC_PHY_BMCR_PWRDN 0x0800 |

Power-down.

Definition at line 150 of file at91_emac.c.

| #define NIC_PHY_BMCR_ANEGENA 0x1000 |

Enable auto negotiation.

Definition at line 151 of file at91_emac.c.

| #define NIC_PHY_BMCR_100MBPS 0x2000 |

Select 100 Mbps.

Definition at line 152 of file at91_emac.c.

| #define NIC_PHY_BMCR_LOOPBACK 0x4000 |

Enable loopback mode.

Definition at line 153 of file at91_emac.c.

| #define NIC_PHY_BMCR_RESET 0x8000 |

Software reset.

Definition at line 154 of file at91_emac.c.

| #define NIC_PHY_BMSR 0x01 |

Basic mode status register.

Definition at line 156 of file at91_emac.c.

| #define NIC_PHY_BMSR_ANCOMPL 0x0020 |

Auto negotiation complete.

Definition at line 157 of file at91_emac.c.

| #define NIC_PHY_BMSR_LINKSTAT 0x0004 |

Link status.

Definition at line 158 of file at91_emac.c.

| #define NIC_PHY_ID1 0x02 |

PHY identifier register 1.

Definition at line 160 of file at91_emac.c.

| #define NIC_PHY_ID2 0x03 |

PHY identifier register 2.

Definition at line 161 of file at91_emac.c.

| #define NIC_PHY_ANAR 0x04 |

Auto negotiation advertisement register.

Definition at line 162 of file at91_emac.c.

| #define NIC_PHY_ANLPAR 0x05 |

Auto negotiation link partner availability register.

Definition at line 163 of file at91_emac.c.

| #define NIC_PHY_ANEG_NP 0x8000 |

Next page available.

Definition at line 164 of file at91_emac.c.

| #define NIC_PHY_ANEG_ACK 0x4000 |

Ability data reception acknowledged.

Definition at line 165 of file at91_emac.c.

| #define NIC_PHY_ANEG_RF 0x2000 |

Remote fault.

Definition at line 166 of file at91_emac.c.

| #define NIC_PHY_ANEG_FCS 0x0400 |

Flow control supported.

Definition at line 167 of file at91_emac.c.

| #define NIC_PHY_ANEG_T4 0x0200 |

100BASE-T4 supported.

Definition at line 168 of file at91_emac.c.

| #define NIC_PHY_ANEG_TX_FDX 0x0100 |

100BASE-T full duplex supported.

Definition at line 169 of file at91_emac.c.

| #define NIC_PHY_ANEG_TX_HDX 0x0080 |

100BASE-T half duplex supported.

Definition at line 170 of file at91_emac.c.

| #define NIC_PHY_ANEG_10_FDX 0x0040 |

10BASE-T full duplex supported.

Definition at line 171 of file at91_emac.c.

| #define NIC_PHY_ANEG_10_HDX 0x0020 |

10BASE-T half duplex supported.

Definition at line 172 of file at91_emac.c.

| #define NIC_PHY_ANEG_BINSEL 0x001F |

Binary encoded protocol selector.

Definition at line 173 of file at91_emac.c.

| #define NIC_PHY_ANER 0x06 |

Auto negotiation expansion register.

Definition at line 175 of file at91_emac.c.

| #define NIC_PHY_BMCR 0x00 |

Basic mode control register.

Definition at line 116 of file at91sam7x_emac.c.

| #define NIC_PHY_BMCR_COLTEST 0x0080 |

Collision test.

Definition at line 117 of file at91sam7x_emac.c.

| #define NIC_PHY_BMCR_FDUPLEX 0x0100 |

Full duplex mode.

Definition at line 118 of file at91sam7x_emac.c.

| #define NIC_PHY_BMCR_ANEGSTART 0x0200 |

Restart auto negotiation.

Definition at line 119 of file at91sam7x_emac.c.

| #define NIC_PHY_BMCR_ISOLATE 0x0400 |

Isolate from MII.

Definition at line 120 of file at91sam7x_emac.c.

| #define NIC_PHY_BMCR_PWRDN 0x0800 |

Power-down.

Definition at line 121 of file at91sam7x_emac.c.

| #define NIC_PHY_BMCR_ANEGENA 0x1000 |

Enable auto negotiation.

Definition at line 122 of file at91sam7x_emac.c.

| #define NIC_PHY_BMCR_100MBPS 0x2000 |

Select 100 Mbps.

Definition at line 123 of file at91sam7x_emac.c.

| #define NIC_PHY_BMCR_LOOPBACK 0x4000 |

Enable loopback mode.

Definition at line 124 of file at91sam7x_emac.c.

| #define NIC_PHY_BMCR_RESET 0x8000 |

Software reset.

Definition at line 125 of file at91sam7x_emac.c.

| #define NIC_PHY_BMSR 0x01 |

Basic mode status register.

Definition at line 127 of file at91sam7x_emac.c.

| #define NIC_PHY_BMSR_ANCOMPL 0x0020 |

Auto negotiation complete.

Definition at line 128 of file at91sam7x_emac.c.

| #define NIC_PHY_BMSR_LINKSTAT 0x0004 |

Link status.

Definition at line 129 of file at91sam7x_emac.c.

| #define NIC_PHY_ID1 0x02 |

PHY identifier register 1.

Definition at line 131 of file at91sam7x_emac.c.

| #define NIC_PHY_ID2 0x03 |

PHY identifier register 2.

Definition at line 132 of file at91sam7x_emac.c.

| #define NIC_PHY_ANAR 0x04 |

Auto negotiation advertisement register.

Definition at line 133 of file at91sam7x_emac.c.

| #define NIC_PHY_ANLPAR 0x05 |

Auto negotiation link partner availability register.

Definition at line 134 of file at91sam7x_emac.c.

| #define NIC_PHY_ANER 0x06 |

Auto negotiation expansion register.

Definition at line 135 of file at91sam7x_emac.c.

| #define NIC_PHY_BMCR_ANEGSTART 0x0200 |

| #define NIC_PHY_BMSR_ANCOMPL 0x0020 |

| #define NIC_PHY_ANAR 0x04 |

| #define NIC_PHY_ANLPAR 0x05 |

| #define NIC_PHY_ANEG_ACK 0x4000 |

| #define NIC_PHY_ANEG_TX_FDX 0x0100 |

| #define NIC_PHY_ANEG_TX_HDX 0x0080 |

| #define NIC_PHY_ANEG_10_FDX 0x0040 |

| #define NIC_PHY_ANEG_10_HDX 0x0020 |

| #define NIC_PHY_ANEG_BINSEL 0x001F |

| #define NIC_PHY_ANER 0x06 |

| #define NIC_PHY_ADVERTISE_CSMA 0x0001 |

| #define NIC_PHY_ADVERTISE_10HALF 0x0020 |

| #define NIC_PHY_ADVERTISE_1000XFULL 0x0020 |

| #define NIC_PHY_ADVERTISE_10FULL 0x0040 |

| #define NIC_PHY_ADVERTISE_1000XHALF 0x0040 |

| #define NIC_PHY_ADVERTISE_100HALF 0x0080 |

| #define NIC_PHY_ADVERTISE_1000XPAUSE 0x0080 |

| #define NIC_PHY_ADVERTISE_100FULL 0x0100 |

| #define NIC_PHY_ADVERTISE_1000XPSE_ASYM 0x0100 |

| #define NIC_PHY_ADVERTISE_100BASE4 0x0200 |

| #define NIC_PHY_ADVERTISE_PAUSE_ASYM 0x0800 |

| #define NIC_PHY_ADVERTISE_RFAULT 0x2000 |

| #define NIC_PHY_ADVERTISE_LPACK 0x4000 |

| #define NIC_PHY_ADVERTISE_FULL (NIC_PHY_ADVERTISE_100FULL | NIC_PHY_ADVERTISE_10FULL | NIC_PHY_ADVERTISE_CSMA) |

| #define NIC_PHY_ADVERTISE_ALL |

(NIC_PHY_ADVERTISE_10HALF | NIC_PHY_ADVERTISE_10FULL | \ NIC_PHY_ADVERTISE_100HALF | NIC_PHY_ADVERTISE_100FULL)

| #define NIC_PHY_ADDR 0 |

| #define PHY_MODE_RMII |

| typedef struct _RxTdDescriptor RxTdDescriptor |

Receive Transfer descriptor structure.