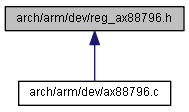

Go to the source code of this file.

| #define | CR 0x00 |

| Asix Ax88796L register definitions. | |

| #define | DATAPORT 0x10 |

| Data Port. | |

| #define | IFGS1 0x12 |

| Inter-frame Gap Segment 1. | |

| #define | IFGS2 0x13 |

| Inter-frame Gap Segment 2. | |

| #define | MII_EEP 0x14 |

| MII/EEPROM Access. | |

| #define | TR 0x15 |

| Test Register. | |

| #define | IFG 0x16 |

| Inter-frame Gap. | |

| #define | GPI 0x17 |

| GPI. | |

| #define | GPOC 0x17 |

| GPOC. | |

| #define | SPP1 0x18 |

| Standard Printer Port 1. | |

| #define | SPP2 0x19 |

| Standard Printer Port 2. | |

| #define | SPP3 0x1a |

| Standard Printer Port 3. | |

| #define | RESET 0x1f |

| Reset port. | |

| #define | PG0_PSTART 0x01 |

| Page start register. | |

| #define | PG0_PSTOP 0x02 |

| Page stop register. | |

| #define | PG0_BNRY 0x03 |

| Boundary pointer. | |

| #define | PG0_TSR 0x04 |

| Transmit status register. | |

| #define | PG0_TPSR 0x04 |

| Transmit page start address. | |

| #define | PG0_NCR 0x05 |

| Number of collisions register. | |

| #define | PG0_TBCR0 0x05 |

| Transmit byte count register 0. | |

| #define | PG0_CPR 0x06 |

| Current Page Register. | |

| #define | PG0_TBCR1 0x06 |

| Transmit Byte Count Register 1. | |

| #define | PG0_ISR 0x07 |

| Interrupt status register. | |

| #define | PG0_CRDA0 0x08 |

| Current remote DMA address 0. | |

| #define | PG0_RSAR0 0x08 |

| Remote start address register 0 Low byte address to read from the buffer. | |

| #define | PG0_CRDA1 0x09 |

| Current remote DMA address 1. | |

| #define | PG0_RSAR1 0x09 |

| Remote start address register 1 High byte address to read from the buffer. | |

| #define | PG0_RBCR0 0x0a |

| Remote byte count register 0 Low byte of the number of bytes to read from the buffer. | |

| #define | PG0_RBCR1 0x0b |

| Remote byte count register 1 High byte of the number of bytes to read from the buffer. | |

| #define | PG0_RSR 0x0c |

| Receive status register. | |

| #define | PG0_RCR 0x0c |

| Receive configuration register. | |

| #define | PG0_CNTR0 0x0d |

| Tally counter 0 (frame alignment errors) | |

| #define | PG0_TCR 0x0d |

| Transmit configuration register. | |

| #define | PG0_DCR 0x0e |

| Data configuration register. | |

| #define | PG0_IMR 0x0f |

| Interrupt mask register. | |

| #define | PG1_PAR0 0x01 |

| Physical Address Register 0. | |

| #define | PG1_PAR1 0x02 |

| Physical Address Register 1. | |

| #define | PG1_PAR2 0x03 |

| Physical Address Register 2. | |

| #define | PG1_PAR3 0x04 |

| Physical Address Register 3. | |

| #define | PG1_PAR4 0x05 |

| Physical Address Register 4. | |

| #define | PG1_PAR5 0x06 |

| Physical Address Register 5. | |

| #define | PG1_CPR 0x07 |

| Current Page Register. | |

| #define | PG1_MAR0 0x08 |

| Multicast Address Register 0. | |

| #define | PG1_MAR1 0x09 |

| Multicast Address Register 1. | |

| #define | PG1_MAR2 0x0a |

| Multicast Address Register 2. | |

| #define | PG1_MAR3 0x0b |

| Multicast Address Register 3. | |

| #define | PG1_MAR4 0x0c |

| Multicast Address Register 4. | |

| #define | PG1_MAR5 0x0d |

| Multicast Address Register 5. | |

| #define | PG1_MAR6 0x0e |

| Multicast Address Register 6. | |

| #define | PG1_MAR7 0x0f |

| Multicast Address Register 7. | |

| #define | CR_STOP 0x01 |

| Stop. | |

| #define | CR_START 0x02 |

| Start. | |

| #define | CR_TXP 0x04 |

| Transmit packet. | |

| #define | CR_RD0 0x08 |

| Remote DMA command bit 0. | |

| #define | CR_RD1 0x10 |

| Remote DMA command bit 1. | |

| #define | CR_RD2 0x20 |

| Remote DMA command bit 2. | |

| #define | CR_PS0 0x40 |

| Page select bit 0. | |

| #define | CR_PS1 0x80 |

| Page select bit 1. | |

| #define | ISR_PRX 0x01 |

| Packet received. | |

| #define | ISR_PTX 0x02 |

| Packet transmitted. | |

| #define | ISR_RXE 0x04 |

| Receive error. | |

| #define | ISR_TXE 0x08 |

| Transmit error. | |

| #define | ISR_OVW 0x10 |

| Overwrite warning. | |

| #define | ISR_CNT 0x20 |

| Counter overflow. | |

| #define | ISR_RDC 0x40 |

| Remote DMA complete. | |

| #define | ISR_RST 0x80 |

| Reset status. | |

| #define | IMR_PRXE 0x01 |

| Packet received interrupt enable. | |

| #define | IMR_PTXE 0x02 |

| Packet transmitted interrupt enable. | |

| #define | IMR_RXEE 0x04 |

| Receive error interrupt enable. | |

| #define | IMR_TXEE 0x08 |

| Transmit error interrupt enable. | |

| #define | IMR_OVWE 0x10 |

| Overwrite warning interrupt enable. | |

| #define | IMR_CNTE 0x20 |

| Counter overflow interrupt enable. | |

| #define | IMR_RCDE 0x40 |

| Remote DMA complete interrupt enable. | |

| #define | DCR_WTS 0x01 |

| Word transfer select. | |

| #define | DCR_RDCR 0x80 |

| Remote DMA always completed. | |

| #define | TCR_CRC 0x01 |

| Inhibit CRC. | |

| #define | TCR_LB0 0x02 |

| Encoded loopback control bit 0. | |

| #define | TCR_LB1 0x04 |

| Encoded loopback control bit 1. | |

| #define | TCR_RLO 0x20 |

| Full Duplex. | |

| #define | TCR_PD 0x40 |

| Pad Disable. | |

| #define | TCR_FDU 0x80 |

| Retry of late collision. | |

| #define | TSR_PTX 0x01 |

| Packet transmitted. | |

| #define | TSR_COL 0x04 |

| Transmit collided. | |

| #define | TSR_ABT 0x08 |

| Transmit aborted. | |

| #define | TSR_OWC 0x80 |

| Out of window collision. | |

| #define | RCR_SEP 0x01 |

| Save errored packets. | |

| #define | RCR_AR 0x02 |

| Accept runt packets. | |

| #define | RCR_AB 0x04 |

| Accept broadcast. | |

| #define | RCR_AM 0x08 |

| Accept multicast. | |

| #define | RCR_PRO 0x10 |

| Promiscuous physical. | |

| #define | RCR_MON 0x20 |

| Monitor mode. | |

| #define | RCR_INTT 0x40 |

| Interrupt Trigger Mode. | |

| #define | RSR_PRX 0x01 |

| Packet received intact. | |

| #define | RSR_CR 0x02 |

| CRC error. | |

| #define | RSR_FAE 0x04 |

| Frame alignment error. | |

| #define | RSR_FO 0x08 |

| FIFO overrun. | |

| #define | RSR_MPA 0x10 |

| Missed packet. | |

| #define | RSR_PHY 0x20 |

| Physical/multicast address. | |

| #define | RSR_DIS 0x40 |

| Receiver disabled. | |

| #define | MII_EEP_MDC 0x01 |

| MII clock. | |

| #define | MII_EEP_MDIR 0x02 |

| MII MDIO directions. | |

| #define | MII_EEP_MDI 0x04 |

| MII data In. | |

| #define | MII_EEP_MDO 0x08 |

| MII data Out. | |

| #define | MII_EEP_EECS 0x10 |

| EEPROM Chip select. | |

| #define | MII_EEP_EEI 0x20 |

| EEPROM data in. | |

| #define | MII_EEP_EEO 0x40 |

| EEPROM data out. | |

| #define | MII_EEP_EECLK 0x80 |

| EEPROM clock. | |

| #define | TR_RST_B 0x02 |

| Reset busy. | |

| #define | PHY_MR0 0x00 |

| Control. | |

| #define | PHY_MR1 0x01 |

| Status. | |

| #define | PHY_MR2 0x02 |

| PHY Identifier 1. | |

| #define | PHY_MR3 0x03 |

| PHY Identifier 2. | |

| #define | PHY_MR4 0x04 |

| Autonegotiation Advertisement. | |

| #define | PHY_MR5 0x05 |

| Autonegotiation Link Partner Ability. | |

| #define | PHY_MR6 0x06 |

| Autonegotiation Expansion. | |

| #define | PHY_MR7 0x07 |

| Next Page Transmit. | |

| #define | PHY_MR16 0x10 |

| PCS Control Register. | |

| #define | PHY_MR17 0x11 |

| Autonegotiation (read register A) | |

| #define | PHY_MR18 0x12 |

| Autonegotiation (read register B) | |

| #define | PHY_MR19 0x13 |

| Analog Test Register. | |

| #define | PHY_MR20 0x14 |

| User-defined Register. | |

| #define | PHY_MR21 0x15 |

| RXER Counter. | |

| #define | PHY_MR22 0x16 |

| Analog Test Registers. | |

| #define | PHY_MR23 0x17 |

| Analog Test Registers. | |

| #define | PHY_MR24 0x18 |

| Analog Test Registers. | |

| #define | PHY_MR25 0x19 |

| Analog Test (tuner) Registers. | |

| #define | PHY_MR26 0x1a |

| Analog Test (tuner) Registers. | |

| #define | PHY_MR27 0x1b |

| Analog Test (tuner) Registers. | |

| #define | PHY_MR28 0x1c |

| Device Specific 1. | |

| #define | PHY_MR29 0x1d |

| Device Specific 2. | |

| #define | PHY_MR30 0x1e |

| Device Specific 3. | |

| #define | PHY_MR31 0x1f |

| Quick Status Register. | |

| #define | MR0_SW_RESET 0x8000 |

| #define | MR0_LOOPBACK 0x4000 |

| #define | MR0_SPEED100 0x2000 |

| #define | MR0_NWAY_ENA 0x1000 |

| #define | MR0_PWRDN 0x0800 |

| #define | MR0_ISOLATE 0x0400 |

| #define | MR0_REDONWAY 0x0200 |

| #define | MR0_FULL_DUP 0x0100 |

| #define | MR0_COLTST 0x0080 |

| #define | MR1_T4ABLE 0x8000 |

| #define | MR1_TXFULDUP 0x4000 |

| #define | MR1_TXHAFDUP 0x2000 |

| #define | MR1_ENFULDUP 0x1000 |

| #define | MR1_ENHAFDUP 0x0800 |

| #define | MR1_NO_PA_OK 0x0040 |

| #define | MR1_NWAYDONE 0x0020 |

| #define | MR1_REM_FLT 0x0010 |

| #define | MR1_NWAYABLE 0x0008 |

| #define | MR1_LSTAT_OK 0x0004 |

| #define | MR1_JABBER 0x0002 |

| #define | MR1_EXT_ABLE 0x0001 |

| #define | MR31_LSTAT_OK 0x0800 |

| #define | MR31_SPEED100 0x0200 |

| #define | MR31_FULL_DUP 0x0100 |

| #define CR 0x00 |

Asix Ax88796L register definitions.

Command register

Definition at line 12 of file reg_ax88796.h.

Referenced by NicPhyRead(), and NicPhyWrite().

| #define DATAPORT 0x10 |

Data Port.

Definition at line 13 of file reg_ax88796.h.

| #define IFGS1 0x12 |

Inter-frame Gap Segment 1.

Definition at line 14 of file reg_ax88796.h.

| #define IFGS2 0x13 |

Inter-frame Gap Segment 2.

Definition at line 15 of file reg_ax88796.h.

| #define MII_EEP 0x14 |

MII/EEPROM Access.

Definition at line 16 of file reg_ax88796.h.

| #define TR 0x15 |

Test Register.

Definition at line 17 of file reg_ax88796.h.

| #define IFG 0x16 |

Inter-frame Gap.

Definition at line 18 of file reg_ax88796.h.

| #define GPI 0x17 |

GPI.

Definition at line 19 of file reg_ax88796.h.

| #define GPOC 0x17 |

GPOC.

Definition at line 20 of file reg_ax88796.h.

| #define SPP1 0x18 |

Standard Printer Port 1.

Definition at line 21 of file reg_ax88796.h.

| #define SPP2 0x19 |

Standard Printer Port 2.

Definition at line 22 of file reg_ax88796.h.

| #define SPP3 0x1a |

Standard Printer Port 3.

Definition at line 23 of file reg_ax88796.h.

| #define RESET 0x1f |

Reset port.

Definition at line 24 of file reg_ax88796.h.

| #define PG0_PSTART 0x01 |

Page start register.

Definition at line 29 of file reg_ax88796.h.

| #define PG0_PSTOP 0x02 |

Page stop register.

Definition at line 30 of file reg_ax88796.h.

| #define PG0_BNRY 0x03 |

Boundary pointer.

Definition at line 31 of file reg_ax88796.h.

| #define PG0_TSR 0x04 |

Transmit status register.

Definition at line 32 of file reg_ax88796.h.

| #define PG0_TPSR 0x04 |

Transmit page start address.

Definition at line 33 of file reg_ax88796.h.

| #define PG0_NCR 0x05 |

Number of collisions register.

Definition at line 34 of file reg_ax88796.h.

| #define PG0_TBCR0 0x05 |

Transmit byte count register 0.

Definition at line 35 of file reg_ax88796.h.

| #define PG0_CPR 0x06 |

Current Page Register.

Definition at line 36 of file reg_ax88796.h.

| #define PG0_TBCR1 0x06 |

Transmit Byte Count Register 1.

Definition at line 37 of file reg_ax88796.h.

| #define PG0_ISR 0x07 |

Interrupt status register.

Definition at line 38 of file reg_ax88796.h.

| #define PG0_CRDA0 0x08 |

Current remote DMA address 0.

Definition at line 39 of file reg_ax88796.h.

| #define PG0_RSAR0 0x08 |

Remote start address register 0 Low byte address to read from the buffer.

Definition at line 40 of file reg_ax88796.h.

| #define PG0_CRDA1 0x09 |

Current remote DMA address 1.

Definition at line 42 of file reg_ax88796.h.

| #define PG0_RSAR1 0x09 |

Remote start address register 1 High byte address to read from the buffer.

Definition at line 43 of file reg_ax88796.h.

| #define PG0_RBCR0 0x0a |

Remote byte count register 0 Low byte of the number of bytes to read from the buffer.

Definition at line 45 of file reg_ax88796.h.

| #define PG0_RBCR1 0x0b |

Remote byte count register 1 High byte of the number of bytes to read from the buffer.

Definition at line 48 of file reg_ax88796.h.

| #define PG0_RSR 0x0c |

Receive status register.

Definition at line 51 of file reg_ax88796.h.

| #define PG0_RCR 0x0c |

Receive configuration register.

Definition at line 52 of file reg_ax88796.h.

| #define PG0_CNTR0 0x0d |

Tally counter 0 (frame alignment errors)

Definition at line 53 of file reg_ax88796.h.

| #define PG0_TCR 0x0d |

Transmit configuration register.

Definition at line 54 of file reg_ax88796.h.

| #define PG0_DCR 0x0e |

Data configuration register.

Definition at line 55 of file reg_ax88796.h.

| #define PG0_IMR 0x0f |

Interrupt mask register.

Definition at line 56 of file reg_ax88796.h.

| #define PG1_PAR0 0x01 |

Physical Address Register 0.

Definition at line 61 of file reg_ax88796.h.

| #define PG1_PAR1 0x02 |

Physical Address Register 1.

Definition at line 62 of file reg_ax88796.h.

| #define PG1_PAR2 0x03 |

Physical Address Register 2.

Definition at line 63 of file reg_ax88796.h.

| #define PG1_PAR3 0x04 |

Physical Address Register 3.

Definition at line 64 of file reg_ax88796.h.

| #define PG1_PAR4 0x05 |

Physical Address Register 4.

Definition at line 65 of file reg_ax88796.h.

| #define PG1_PAR5 0x06 |

Physical Address Register 5.

Definition at line 66 of file reg_ax88796.h.

| #define PG1_CPR 0x07 |

Current Page Register.

Definition at line 67 of file reg_ax88796.h.

| #define PG1_MAR0 0x08 |

Multicast Address Register 0.

Definition at line 68 of file reg_ax88796.h.

| #define PG1_MAR1 0x09 |

Multicast Address Register 1.

Definition at line 69 of file reg_ax88796.h.

| #define PG1_MAR2 0x0a |

Multicast Address Register 2.

Definition at line 70 of file reg_ax88796.h.

| #define PG1_MAR3 0x0b |

Multicast Address Register 3.

Definition at line 71 of file reg_ax88796.h.

| #define PG1_MAR4 0x0c |

Multicast Address Register 4.

Definition at line 72 of file reg_ax88796.h.

| #define PG1_MAR5 0x0d |

Multicast Address Register 5.

Definition at line 73 of file reg_ax88796.h.

| #define PG1_MAR6 0x0e |

Multicast Address Register 6.

Definition at line 74 of file reg_ax88796.h.

| #define PG1_MAR7 0x0f |

Multicast Address Register 7.

Definition at line 75 of file reg_ax88796.h.

| #define CR_STOP 0x01 |

Stop.

Definition at line 80 of file reg_ax88796.h.

| #define CR_START 0x02 |

Start.

Definition at line 81 of file reg_ax88796.h.

| #define CR_TXP 0x04 |

Transmit packet.

Definition at line 82 of file reg_ax88796.h.

| #define CR_RD0 0x08 |

Remote DMA command bit 0.

Definition at line 83 of file reg_ax88796.h.

| #define CR_RD1 0x10 |

Remote DMA command bit 1.

Definition at line 84 of file reg_ax88796.h.

| #define CR_RD2 0x20 |

Remote DMA command bit 2.

Definition at line 85 of file reg_ax88796.h.

| #define CR_PS0 0x40 |

Page select bit 0.

Definition at line 86 of file reg_ax88796.h.

Referenced by NicPhyRead(), and NicPhyWrite().

| #define CR_PS1 0x80 |

Page select bit 1.

Definition at line 87 of file reg_ax88796.h.

| #define ISR_PRX 0x01 |

Packet received.

Definition at line 92 of file reg_ax88796.h.

| #define ISR_PTX 0x02 |

Packet transmitted.

Definition at line 93 of file reg_ax88796.h.

| #define ISR_RXE 0x04 |

Receive error.

Definition at line 94 of file reg_ax88796.h.

| #define ISR_TXE 0x08 |

Transmit error.

Definition at line 95 of file reg_ax88796.h.

| #define ISR_OVW 0x10 |

Overwrite warning.

Definition at line 96 of file reg_ax88796.h.

| #define ISR_CNT 0x20 |

Counter overflow.

Definition at line 97 of file reg_ax88796.h.

| #define ISR_RDC 0x40 |

Remote DMA complete.

Definition at line 98 of file reg_ax88796.h.

| #define ISR_RST 0x80 |

Reset status.

Definition at line 99 of file reg_ax88796.h.

| #define IMR_PRXE 0x01 |

Packet received interrupt enable.

Definition at line 104 of file reg_ax88796.h.

| #define IMR_PTXE 0x02 |

Packet transmitted interrupt enable.

Definition at line 105 of file reg_ax88796.h.

| #define IMR_RXEE 0x04 |

Receive error interrupt enable.

Definition at line 106 of file reg_ax88796.h.

| #define IMR_TXEE 0x08 |

Transmit error interrupt enable.

Definition at line 107 of file reg_ax88796.h.

| #define IMR_OVWE 0x10 |

Overwrite warning interrupt enable.

Definition at line 108 of file reg_ax88796.h.

| #define IMR_CNTE 0x20 |

Counter overflow interrupt enable.

Definition at line 109 of file reg_ax88796.h.

| #define IMR_RCDE 0x40 |

Remote DMA complete interrupt enable.

Definition at line 110 of file reg_ax88796.h.

| #define DCR_WTS 0x01 |

Word transfer select.

Definition at line 116 of file reg_ax88796.h.

| #define DCR_RDCR 0x80 |

Remote DMA always completed.

Definition at line 117 of file reg_ax88796.h.

| #define TCR_CRC 0x01 |

Inhibit CRC.

Definition at line 122 of file reg_ax88796.h.

| #define TCR_LB0 0x02 |

Encoded loopback control bit 0.

Definition at line 123 of file reg_ax88796.h.

| #define TCR_LB1 0x04 |

Encoded loopback control bit 1.

Definition at line 124 of file reg_ax88796.h.

| #define TCR_RLO 0x20 |

Full Duplex.

Definition at line 125 of file reg_ax88796.h.

| #define TCR_PD 0x40 |

Pad Disable.

Definition at line 126 of file reg_ax88796.h.

| #define TCR_FDU 0x80 |

Retry of late collision.

Definition at line 127 of file reg_ax88796.h.

| #define TSR_PTX 0x01 |

Packet transmitted.

Definition at line 132 of file reg_ax88796.h.

| #define TSR_COL 0x04 |

Transmit collided.

Definition at line 133 of file reg_ax88796.h.

| #define TSR_ABT 0x08 |

Transmit aborted.

Definition at line 134 of file reg_ax88796.h.

| #define TSR_OWC 0x80 |

Out of window collision.

Definition at line 135 of file reg_ax88796.h.

| #define RCR_SEP 0x01 |

Save errored packets.

Definition at line 140 of file reg_ax88796.h.

| #define RCR_AR 0x02 |

Accept runt packets.

Definition at line 141 of file reg_ax88796.h.

| #define RCR_AB 0x04 |

Accept broadcast.

Definition at line 142 of file reg_ax88796.h.

| #define RCR_AM 0x08 |

Accept multicast.

Definition at line 143 of file reg_ax88796.h.

| #define RCR_PRO 0x10 |

Promiscuous physical.

Definition at line 144 of file reg_ax88796.h.

| #define RCR_MON 0x20 |

Monitor mode.

Definition at line 145 of file reg_ax88796.h.

| #define RCR_INTT 0x40 |

Interrupt Trigger Mode.

Definition at line 146 of file reg_ax88796.h.

| #define RSR_PRX 0x01 |

Packet received intact.

Definition at line 151 of file reg_ax88796.h.

| #define RSR_CR 0x02 |

CRC error.

Definition at line 152 of file reg_ax88796.h.

| #define RSR_FAE 0x04 |

Frame alignment error.

Definition at line 153 of file reg_ax88796.h.

| #define RSR_FO 0x08 |

FIFO overrun.

Definition at line 154 of file reg_ax88796.h.

| #define RSR_MPA 0x10 |

Missed packet.

Definition at line 155 of file reg_ax88796.h.

| #define RSR_PHY 0x20 |

Physical/multicast address.

Definition at line 156 of file reg_ax88796.h.

| #define RSR_DIS 0x40 |

Receiver disabled.

Definition at line 157 of file reg_ax88796.h.

| #define MII_EEP_MDC 0x01 |

MII clock.

Definition at line 162 of file reg_ax88796.h.

| #define MII_EEP_MDIR 0x02 |

MII MDIO directions.

Definition at line 163 of file reg_ax88796.h.

| #define MII_EEP_MDI 0x04 |

MII data In.

Definition at line 164 of file reg_ax88796.h.

| #define MII_EEP_MDO 0x08 |

MII data Out.

Definition at line 165 of file reg_ax88796.h.

| #define MII_EEP_EECS 0x10 |

EEPROM Chip select.

Definition at line 166 of file reg_ax88796.h.

| #define MII_EEP_EEI 0x20 |

EEPROM data in.

Definition at line 167 of file reg_ax88796.h.

| #define MII_EEP_EEO 0x40 |

EEPROM data out.

Definition at line 168 of file reg_ax88796.h.

| #define MII_EEP_EECLK 0x80 |

EEPROM clock.

Definition at line 169 of file reg_ax88796.h.

| #define TR_RST_B 0x02 |

Reset busy.

Definition at line 174 of file reg_ax88796.h.

| #define PHY_MR0 0x00 |

Control.

Definition at line 181 of file reg_ax88796.h.

| #define PHY_MR1 0x01 |

Status.

Definition at line 182 of file reg_ax88796.h.

| #define PHY_MR2 0x02 |

PHY Identifier 1.

Definition at line 183 of file reg_ax88796.h.

| #define PHY_MR3 0x03 |

PHY Identifier 2.

Definition at line 184 of file reg_ax88796.h.

| #define PHY_MR4 0x04 |

Autonegotiation Advertisement.

Definition at line 185 of file reg_ax88796.h.

| #define PHY_MR5 0x05 |

Autonegotiation Link Partner Ability.

Definition at line 186 of file reg_ax88796.h.

| #define PHY_MR6 0x06 |

Autonegotiation Expansion.

Definition at line 187 of file reg_ax88796.h.

| #define PHY_MR7 0x07 |

Next Page Transmit.

Definition at line 188 of file reg_ax88796.h.

| #define PHY_MR16 0x10 |

PCS Control Register.

Definition at line 189 of file reg_ax88796.h.

| #define PHY_MR17 0x11 |

Autonegotiation (read register A)

Definition at line 190 of file reg_ax88796.h.

| #define PHY_MR18 0x12 |

Autonegotiation (read register B)

Definition at line 191 of file reg_ax88796.h.

| #define PHY_MR19 0x13 |

Analog Test Register.

Definition at line 192 of file reg_ax88796.h.

| #define PHY_MR20 0x14 |

User-defined Register.

Definition at line 193 of file reg_ax88796.h.

| #define PHY_MR21 0x15 |

RXER Counter.

Definition at line 194 of file reg_ax88796.h.

| #define PHY_MR22 0x16 |

Analog Test Registers.

Definition at line 195 of file reg_ax88796.h.

| #define PHY_MR23 0x17 |

Analog Test Registers.

Definition at line 196 of file reg_ax88796.h.

| #define PHY_MR24 0x18 |

Analog Test Registers.

Definition at line 197 of file reg_ax88796.h.

| #define PHY_MR25 0x19 |

Analog Test (tuner) Registers.

Definition at line 198 of file reg_ax88796.h.

| #define PHY_MR26 0x1a |

Analog Test (tuner) Registers.

Definition at line 199 of file reg_ax88796.h.

| #define PHY_MR27 0x1b |

Analog Test (tuner) Registers.

Definition at line 200 of file reg_ax88796.h.

| #define PHY_MR28 0x1c |

Device Specific 1.

Definition at line 201 of file reg_ax88796.h.

| #define PHY_MR29 0x1d |

Device Specific 2.

Definition at line 202 of file reg_ax88796.h.

| #define PHY_MR30 0x1e |

Device Specific 3.

Definition at line 203 of file reg_ax88796.h.

| #define PHY_MR31 0x1f |

Quick Status Register.

Definition at line 204 of file reg_ax88796.h.

| #define MR0_SW_RESET 0x8000 |

Definition at line 209 of file reg_ax88796.h.

| #define MR0_LOOPBACK 0x4000 |

Definition at line 210 of file reg_ax88796.h.

| #define MR0_SPEED100 0x2000 |

Definition at line 211 of file reg_ax88796.h.

| #define MR0_NWAY_ENA 0x1000 |

Definition at line 212 of file reg_ax88796.h.

| #define MR0_PWRDN 0x0800 |

Definition at line 213 of file reg_ax88796.h.

| #define MR0_ISOLATE 0x0400 |

Definition at line 214 of file reg_ax88796.h.

| #define MR0_REDONWAY 0x0200 |

Definition at line 215 of file reg_ax88796.h.

| #define MR0_FULL_DUP 0x0100 |

Definition at line 216 of file reg_ax88796.h.

| #define MR0_COLTST 0x0080 |

Definition at line 217 of file reg_ax88796.h.

| #define MR1_T4ABLE 0x8000 |

Definition at line 222 of file reg_ax88796.h.

| #define MR1_TXFULDUP 0x4000 |

Definition at line 223 of file reg_ax88796.h.

| #define MR1_TXHAFDUP 0x2000 |

Definition at line 224 of file reg_ax88796.h.

| #define MR1_ENFULDUP 0x1000 |

Definition at line 225 of file reg_ax88796.h.

| #define MR1_ENHAFDUP 0x0800 |

Definition at line 226 of file reg_ax88796.h.

| #define MR1_NO_PA_OK 0x0040 |

Definition at line 227 of file reg_ax88796.h.

| #define MR1_NWAYDONE 0x0020 |

Definition at line 228 of file reg_ax88796.h.

| #define MR1_REM_FLT 0x0010 |

Definition at line 229 of file reg_ax88796.h.

| #define MR1_NWAYABLE 0x0008 |

Definition at line 230 of file reg_ax88796.h.

| #define MR1_LSTAT_OK 0x0004 |

Definition at line 231 of file reg_ax88796.h.

| #define MR1_JABBER 0x0002 |

Definition at line 232 of file reg_ax88796.h.

| #define MR1_EXT_ABLE 0x0001 |

Definition at line 233 of file reg_ax88796.h.

| #define MR31_LSTAT_OK 0x0800 |

Definition at line 239 of file reg_ax88796.h.

| #define MR31_SPEED100 0x0200 |

Definition at line 240 of file reg_ax88796.h.

| #define MR31_FULL_DUP 0x0100 |

Definition at line 241 of file reg_ax88796.h.